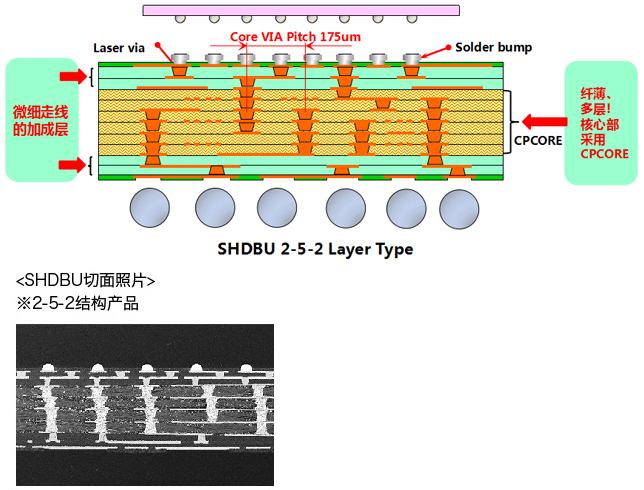

・通过搭配使用高密度全层叠孔载板(CPCORE),提高了Z轴的布线自由度

・通过提高正反面的布线率减少加成层(Buildup)层数

・可确保用于高速宏(macro)内置ASIC的高速信号层

・优良的电气特性也可满足GHz以上高频

・也可满足0.8mm间距以下的Full Area Array BGA

| 项目 | 规格(Unit:μm) | |

| Build up Layer Structure | Up to 4-n-4 | |

| Core Layer Structure | 5 ~ 25 | |

| Build up Line Width / Space | 9 / 12 | |

| Core Line Width / Space | 40 / 40 | |

| Flip Chip Pad Pitch | 125 |

*该数据可能会在无预先通告情况下发生变动。

・高端ASIC、系统LSI

有效利用高频特性优良PPE树脂core层,实现稳定的特性阻抗控制。

通过180根线的实际测量,可验证其阻抗控制在了50Ω ± 5%。

市场领域

产品展示